文章来自:https://www.servethehome.com/sifive-p870-risc-v-processor-at-hot-chips-2023/

原标题:SiFive P870 RISC-V Processor at Hot Chips 2023

SiFive has been a major RISC-V player for the past few years. At Hot Chips 2023, the company went into the SiFive P870 processor in quite a bit of detail.

SiFive 在过去几年中一直是 RISC-V 的主要参与者。 在 Hot Chips 2023 上,该公司相当详细地介绍了 SiFive P870 处理器。(编者:偶尔有朋友提到或混淆“Sifive”和“Starfive", 这两家公司也许当初有一段蜜月期,但今天他们基本就是IP vendor(Sifive)和客户SoC IDH(Starfive,中文名称:赛昉,中国公司)的关系了。另外还有一家名为LeapFive(中文名称:跃昉)的中国公司,这里就不太多八卦了)。

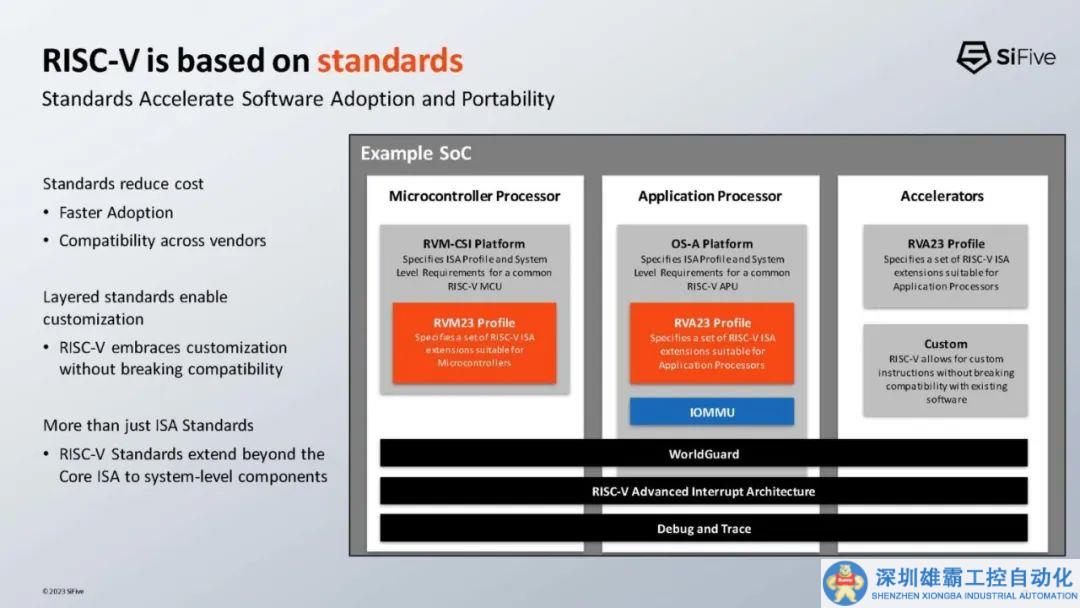

The new RISC-V CPU has standards. That is a big part of the SiFive messaging.

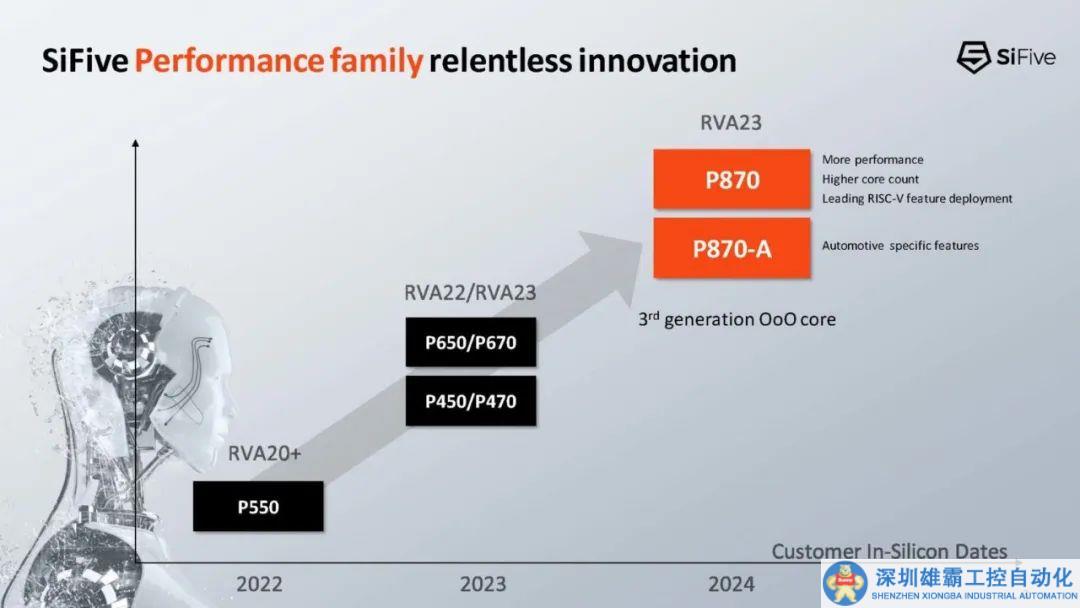

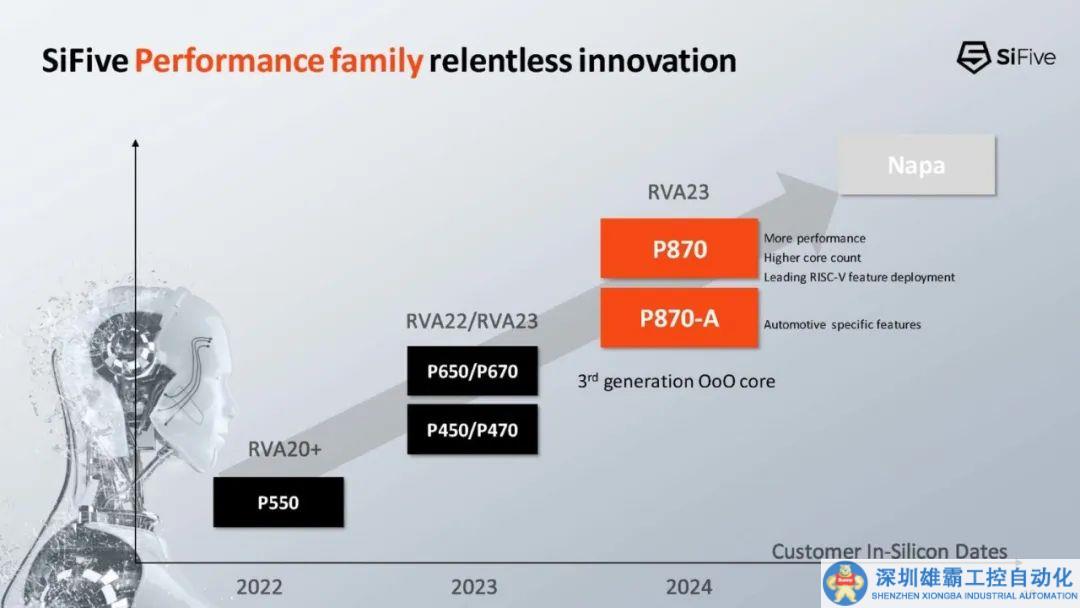

SiFive had its first out-of-order chip in the P550 in 2022. The company now has P650/P670 and the P450/P470. Now, there is the P870 and P870-A. A is for Automotive here.

SiFive 于 2022 年在 P550 中推出了首款乱序芯片。该公司现在拥有 P650/P670 和 P450/P470。 现在,有 P870 和 P870-A。 这里的 A 代表汽车。

(编者:在SOHPGO推出了基于平头哥的C910V的多核处理器后,将在它的下一代芯片中将考虑采用Sifive的P670。平头哥的内耗正在将一手好牌打的稀烂?)

SiFive P870 RISC V HC35_Page_03

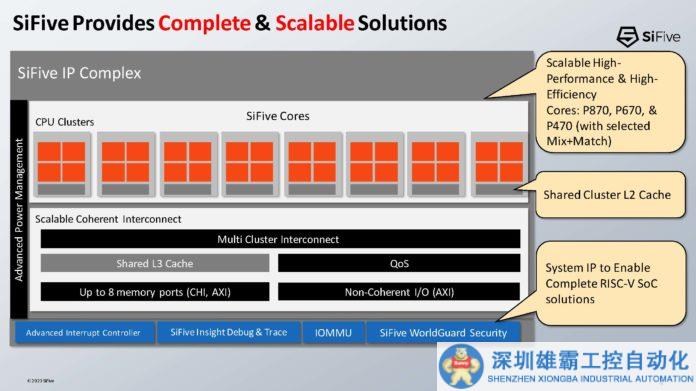

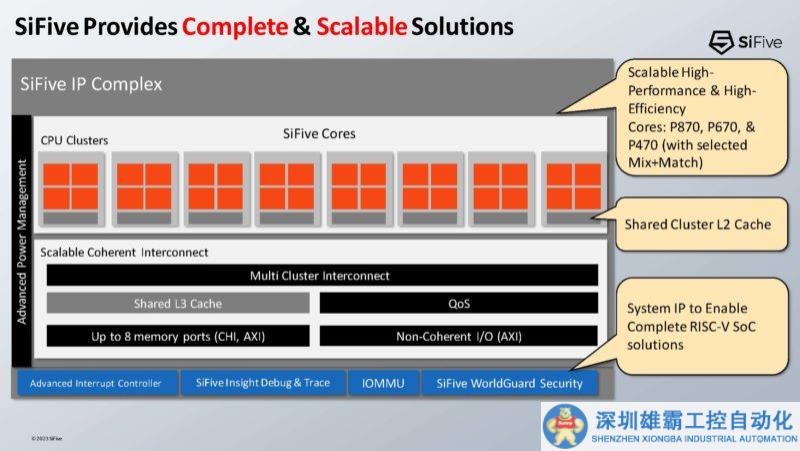

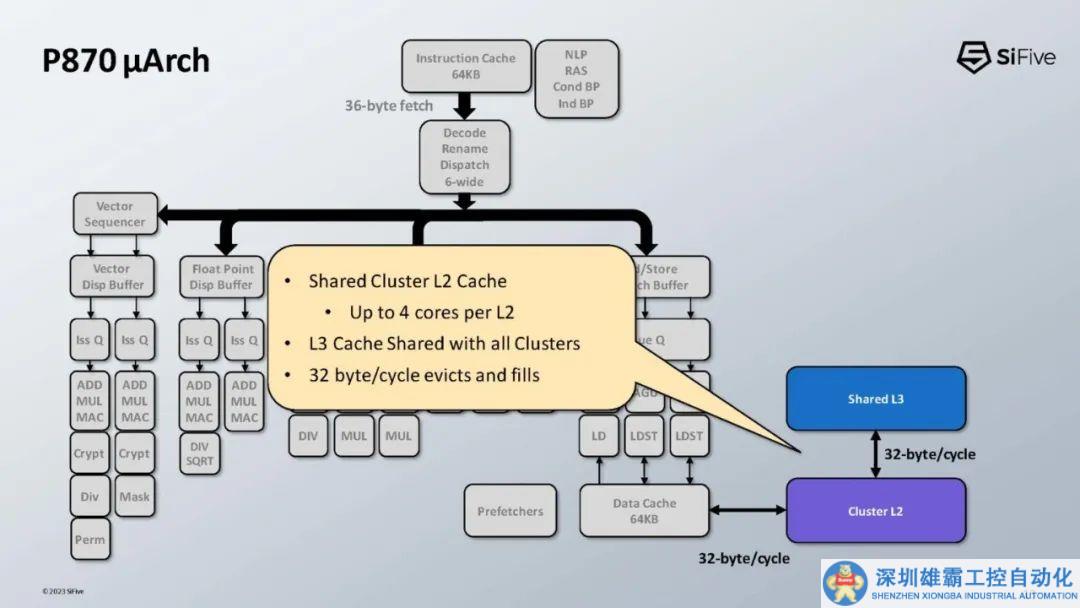

SiFive is building larger and more complex chips now. Something that is different is that the solution utilizes a shared L2 cache. Many Arm CPUs today are working on dedicated L2 caches for cloud workloads.

SiFive 现在正在制造更大、更复杂的芯片。 不同之处在于该解决方案利用共享 L2 缓存。 如今,许多 Arm CPU 都在为云工作负载提供专用的二级缓存。

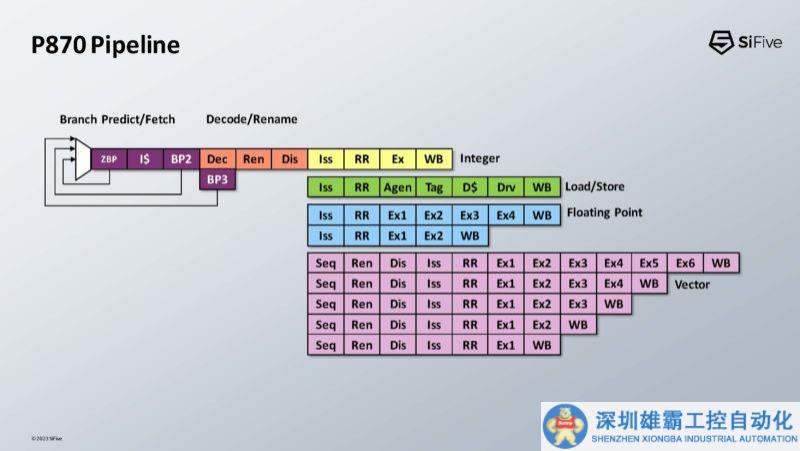

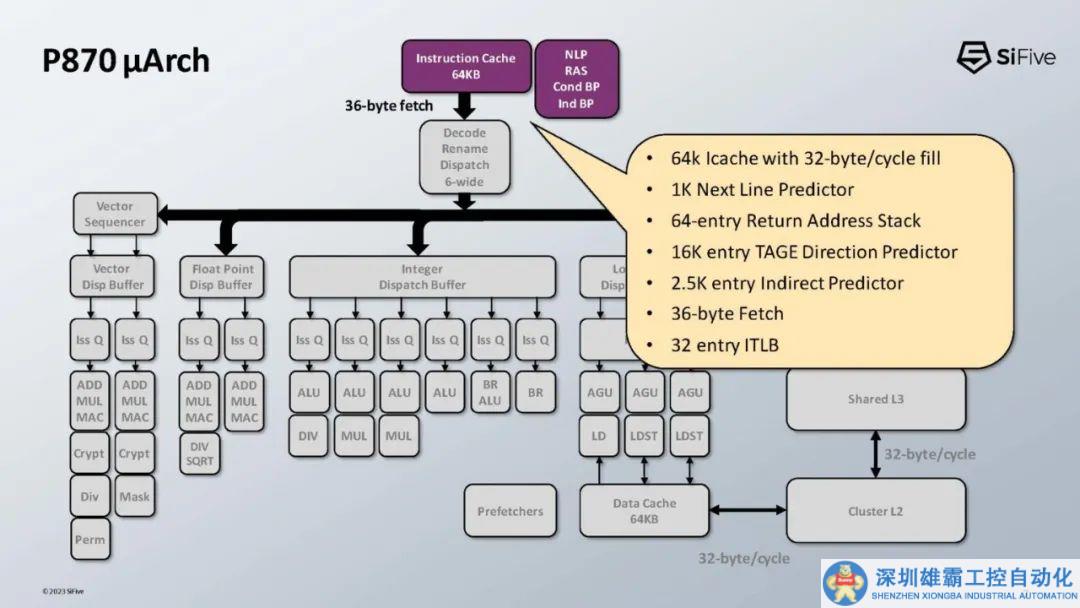

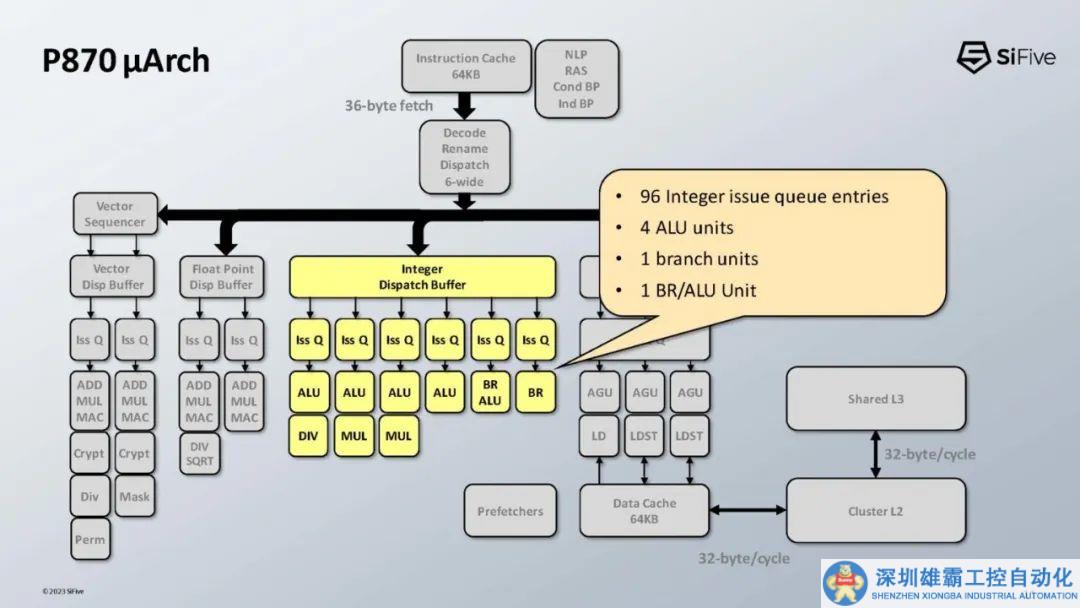

Here is the pipeline.

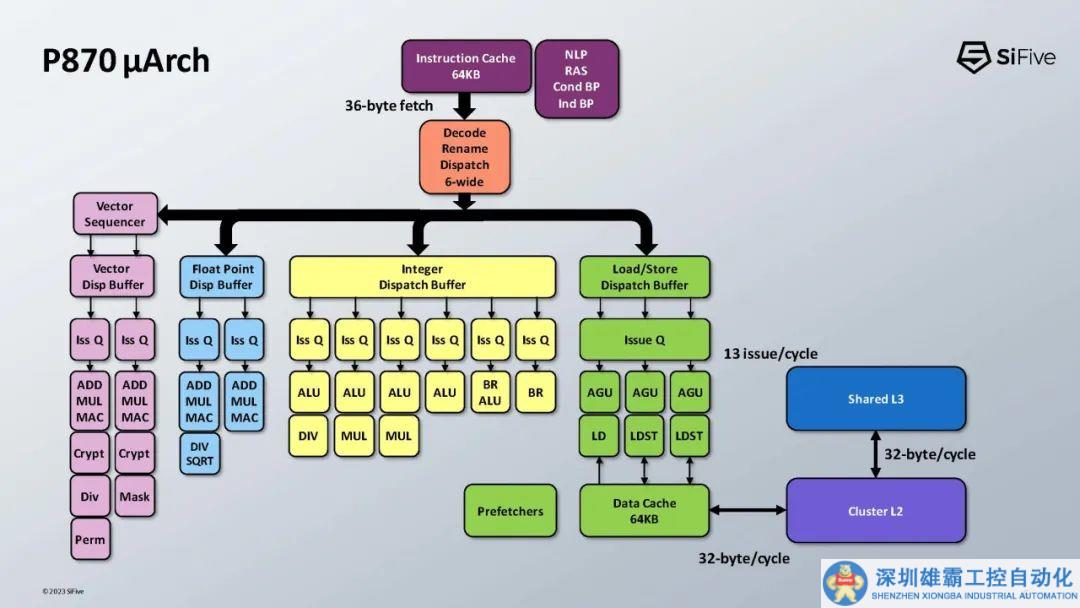

Here is the microarchitecture of the chip. This is more of an instruction flow diagram.

Here is the start of the walk-through on this one starting at the top.

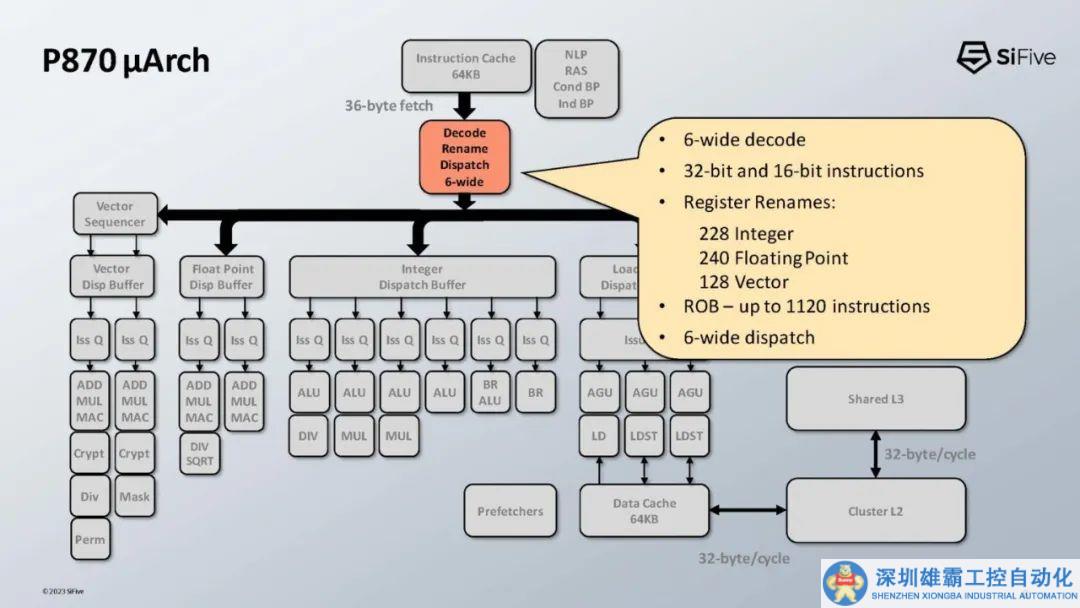

Here SiFive is handling fusion functions here and the ROB of 1120 is being noted as an extreme case. This is basically counting bundled instructions from what it sounds like (maybe this is comparable to 280 in other architectures.)

这里 SiFive 正在处理融合函数,1120 的 ROB 被认为是一个极端情况。 这听起来基本上是捆绑指令(也许这与其他架构中的 280 条指令相当)。

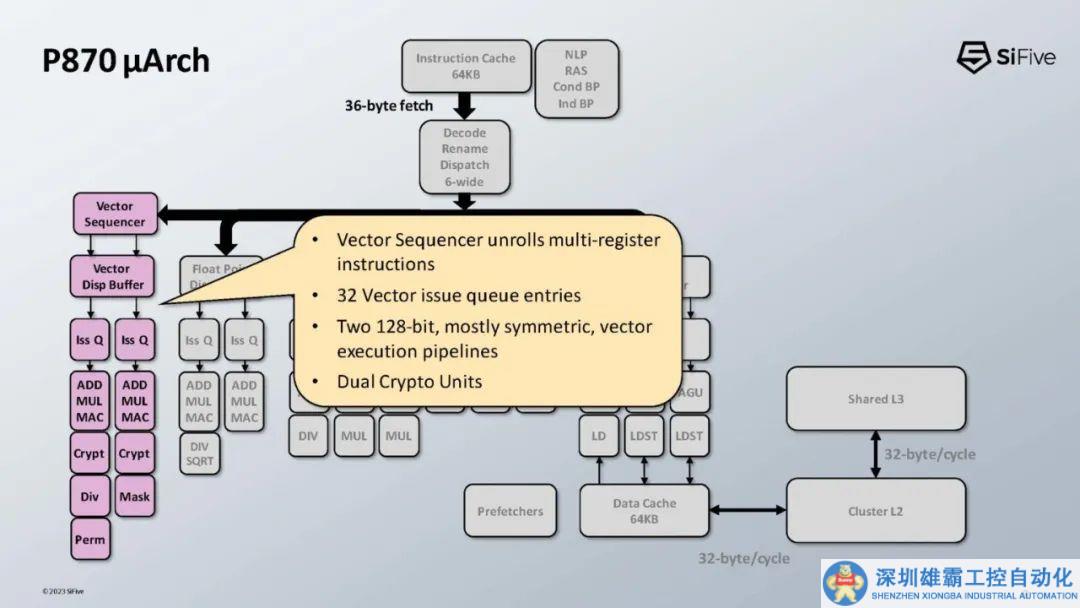

The vector sequencer is being noted as a bit of a unique feature for RISC-V.

Just noting at this point that this is more complex than SiFive’s old solutions.

此时请注意,这比 SiFive 的旧解决方案更复杂。

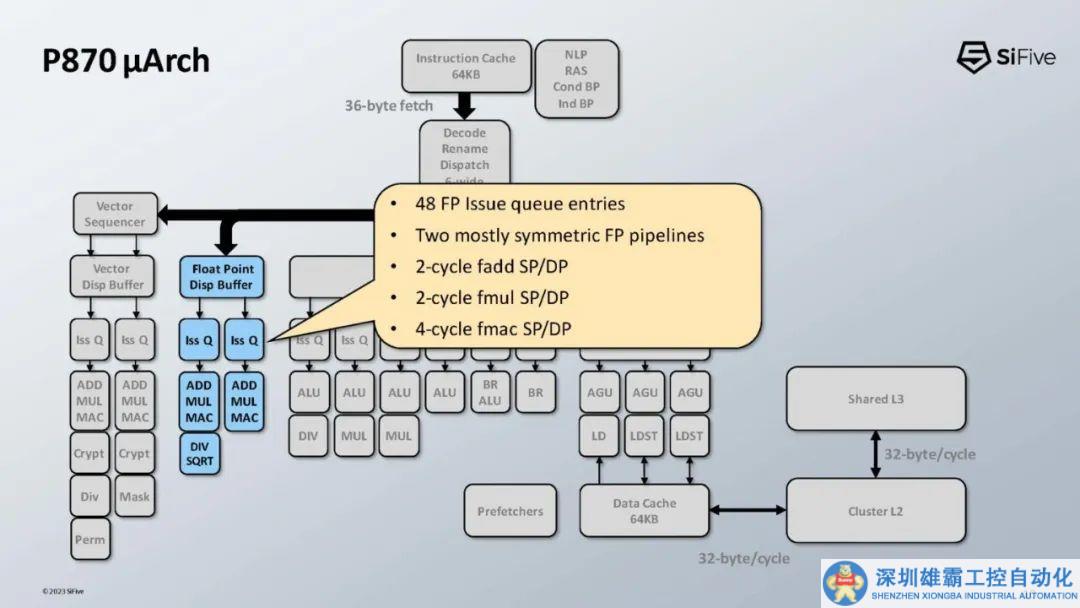

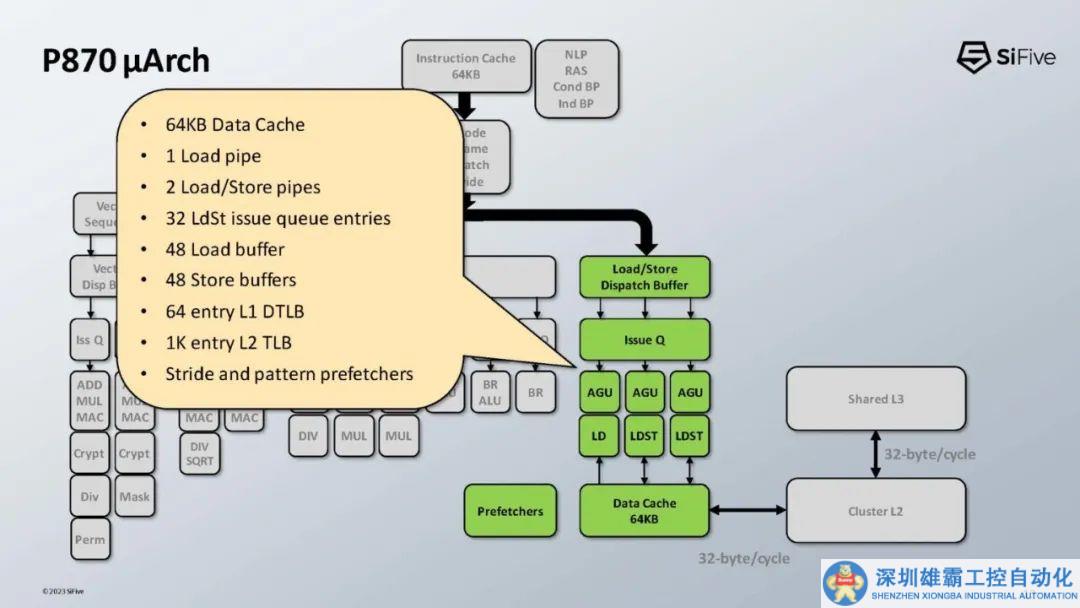

Still going with more microarchitecture details that one can read.

Here are the specs on the load/ store.

L2 cache is non-inclusive but not exclusive.

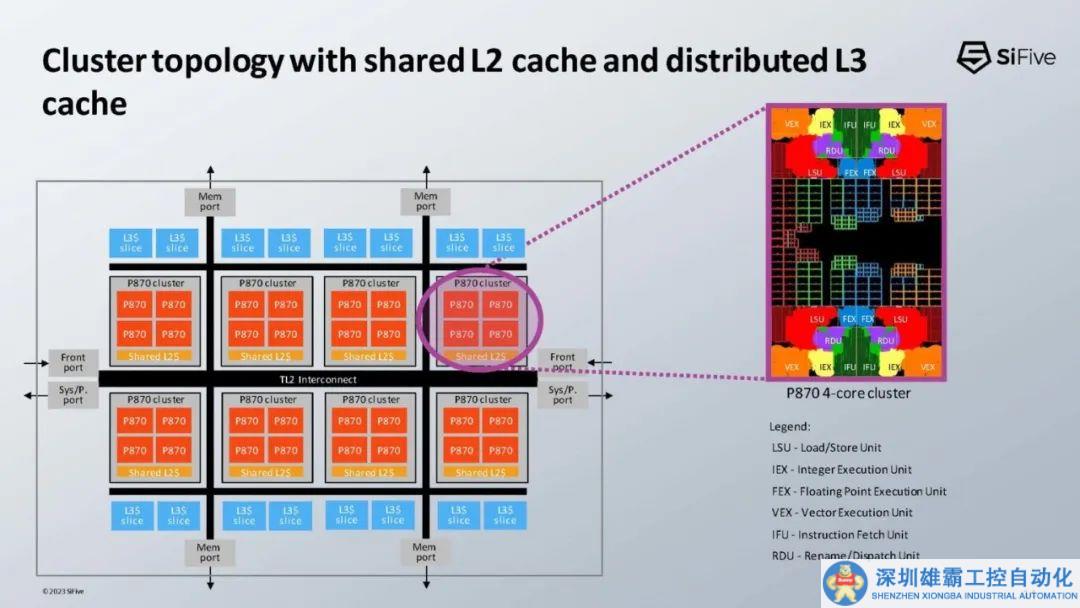

Here is what the cluster topology looks like. L1 with 16-cycle latency to a larger L2. This is designed for data sharing between cores in the cluster. This is a 32-core chip example with 8x 4-core clusters.

这是集群拓扑的样子。 L1 到更大的 L2 具有 16 个周期的延迟。 这是为集群中的核心之间的数据共享而设计的。 这是一个具有 8 个 4 核集群的 32 核芯片示例。

Here is a consumer topology with two P870 higher-performance cores, four P470’s, smaller more efficient cores in a cluster, and then a low-power E6 in-order core for always-on at low power.

这是一个消费类拓扑,其中有两个 P870 高性能核心、四个 P470、集群中更小、更高效的核心,然后是一个低功耗 E6 有序核心,可在低功耗下始终开启。

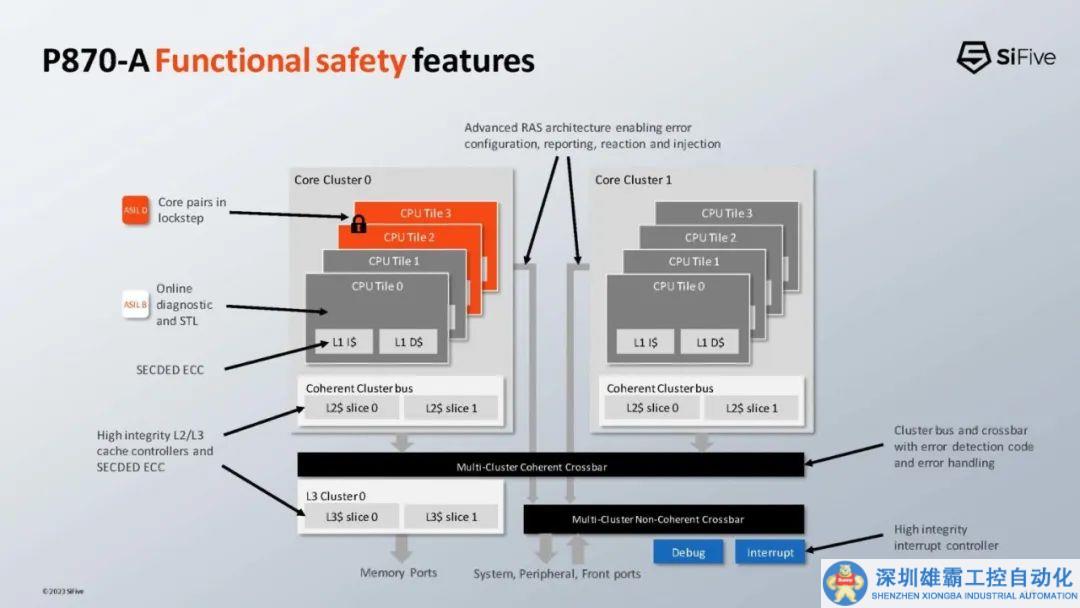

Here is the new SiFive P870-A automotive safety feature slide. Here more focus is on fault detection, reliability, and safety. The P870-A has things like parity in register files, and the caches have ECC as some examples of how this is different.

这是新型 SiFive P870-A 汽车安全功能幻灯片。 这里更关注的是故障检测、可靠性和安全性。 P870-A 在寄存器文件中具有奇偶校验等功能,并且缓存具有 ECC 功能,这可以作为其不同之处的一些示例。

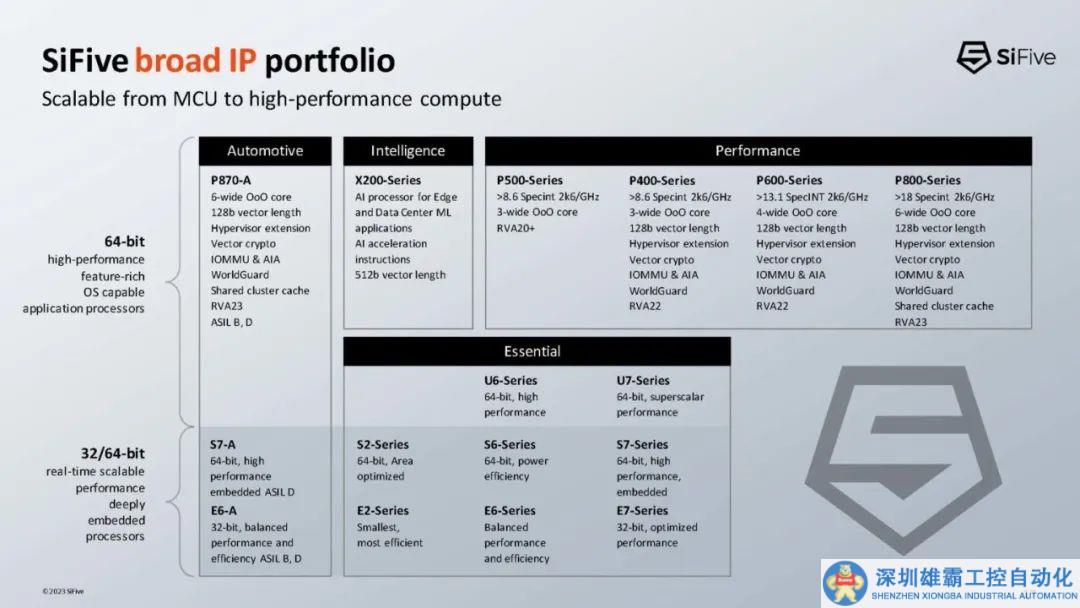

SiFive has a number of different types of IP. Here is a full list. Before seeing this list, I had no idea they had this variety of IP.

这是SiFive多种不同类型的 IP完整列表。 在看到这个列表之前,我不知道他们有这么多的 IP。

The next generation that we will hear about is the Napa core.

我们将听到的下一代是 Napa 核心。

This is not a product announcement. The product announcement will be in a few weeks apparently and the clock speeds are expected to be in the 3GHz range. This was cool to hear about. RISC-V has a lot of momentum and SiFive has been a big player. SiFive is almost starting to feel like it is trying to become the Arm of the RISC-V market but with RISC-V as an ecosystem being open.

这不是产品公告。 该产品显然将在几周内发布,时钟速度预计将在 3GHz 范围内。 听到这个消息真是太酷了。 RISC-V 发展势头强劲,SiFive 一直是其中的重要参与者。 SiFive 几乎开始让人感觉它正在试图成为 RISC-V 市场的手臂,但 RISC-V 作为一个开放的生态系统。

18030183032